Air-/-Plane® technology is a set of proprietary design techniques to achieve leading edge in high-speed performance while keeping cost increase as low as possible.

This section presents just a few examples of Comtel’s leading-edge technology and engineering achievements. We continue research in the areas of interest to stay competitive and push the technology edge and market boundaries.

Goal: Air-/-Plane technology is a set of proprietary design techniques to achieve leading edge in high-speed performance while keeping cost increase as low as possible.

Air-/-Plane® technology is a set of proprietary design techniques to achieve leading edge in high-speed performance while keeping cost increase as low as possible.

Goal: Achieve continuous cost reduction to extend the product life cycle of a custom ATCA backplane.

Goal: achieve continuous cost reduction to extend the product life cycle of a custom ATCA backplane.

Challenge: apply recent research findings in practice

Result: unit cost reduced by 15%

How it was done:

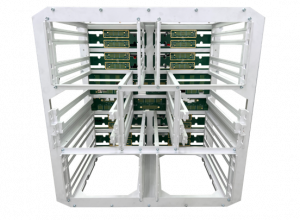

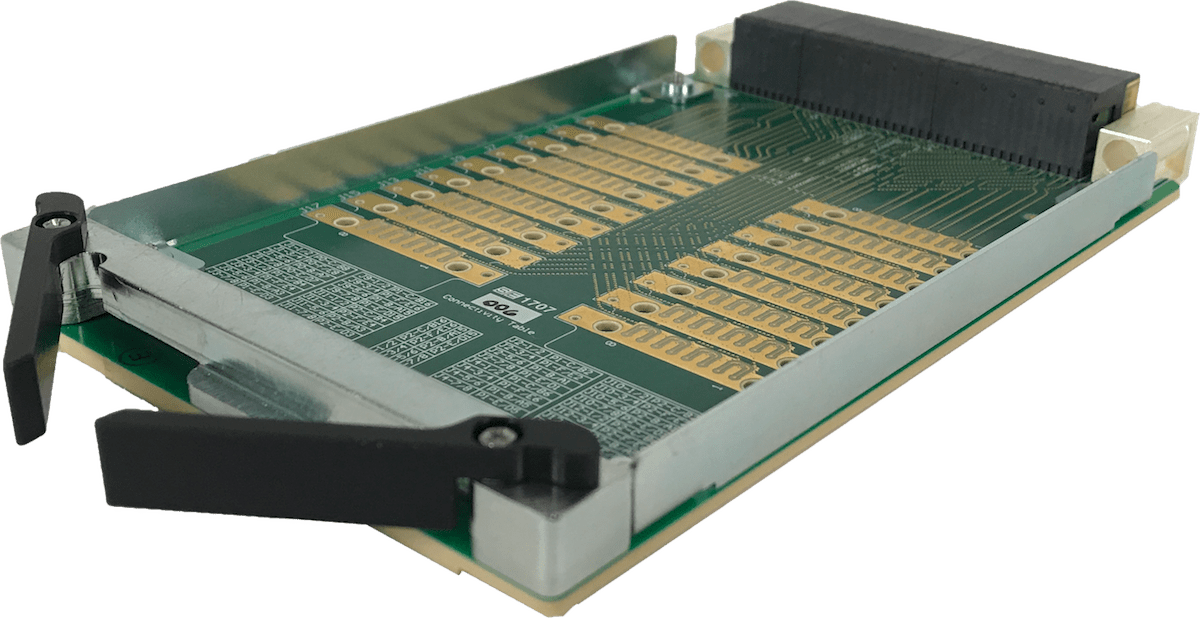

Goal: Customize standard 14 slot ATCA chassis to accept enlarged RTM cards that communicate to the front ATCA cards via the common midplane.

Goal: customize standard 14 slot ATCA chassis to accept enlarged RTM cards that communicate to the front ATCA cards via the common midplane.

Challenge:

Result: first prototypes were available within 6 months which passed customer’s validation without any significant issues

How it was done:

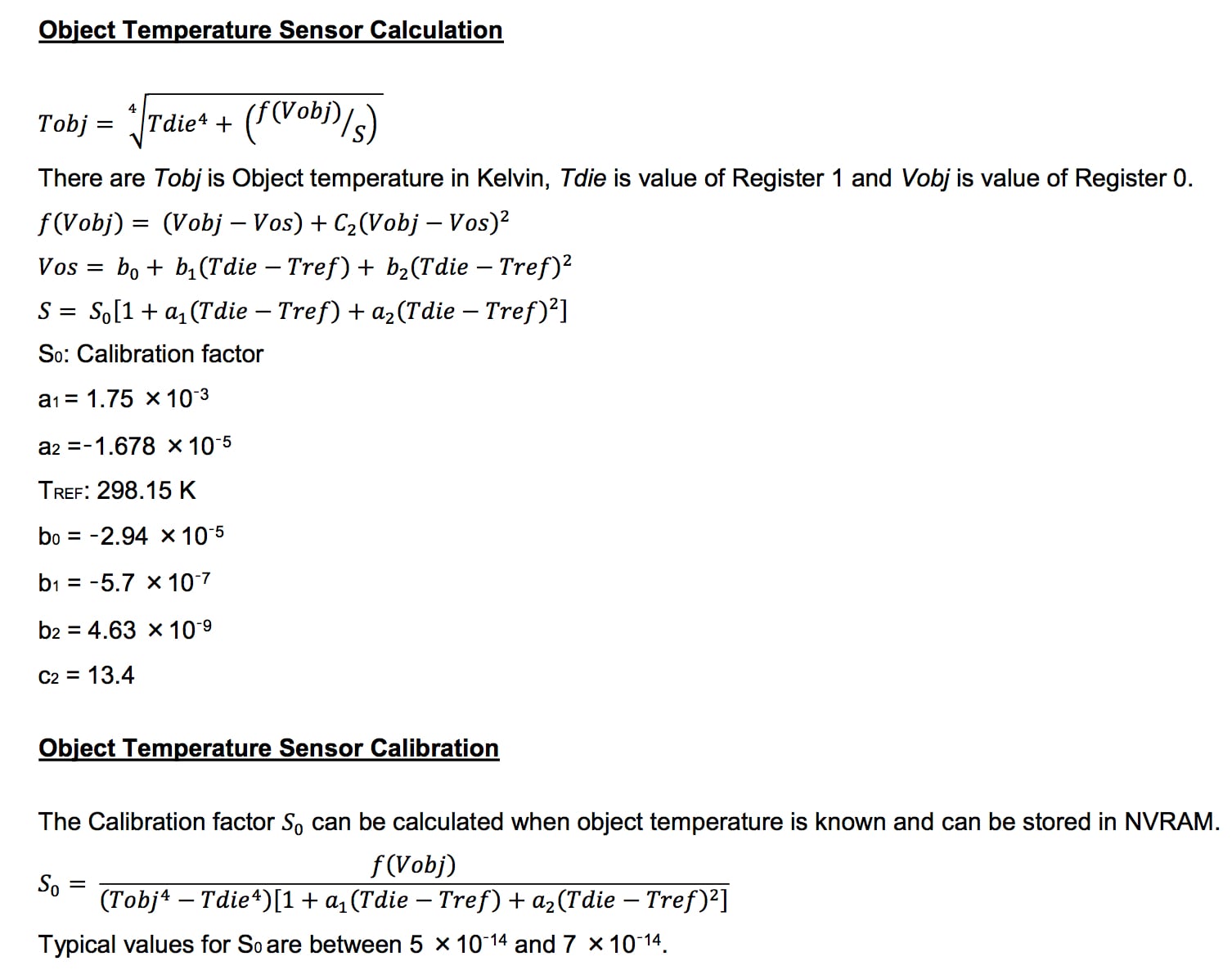

Goal: Design a cost-effective chassis monitoring solution with a contactless temperature measurement of a CPU blade.

Challenge:

Result: met customer’s technical and commercial expectations

How it was done:

Goal: Design a custom backplane simultaneously to customer’s system development

Goal: design a custom backplane simultaneously to customer’s system development

Challenge:

Result: system performance passed validation both by simulation and measurements

How it was done:

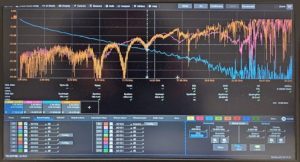

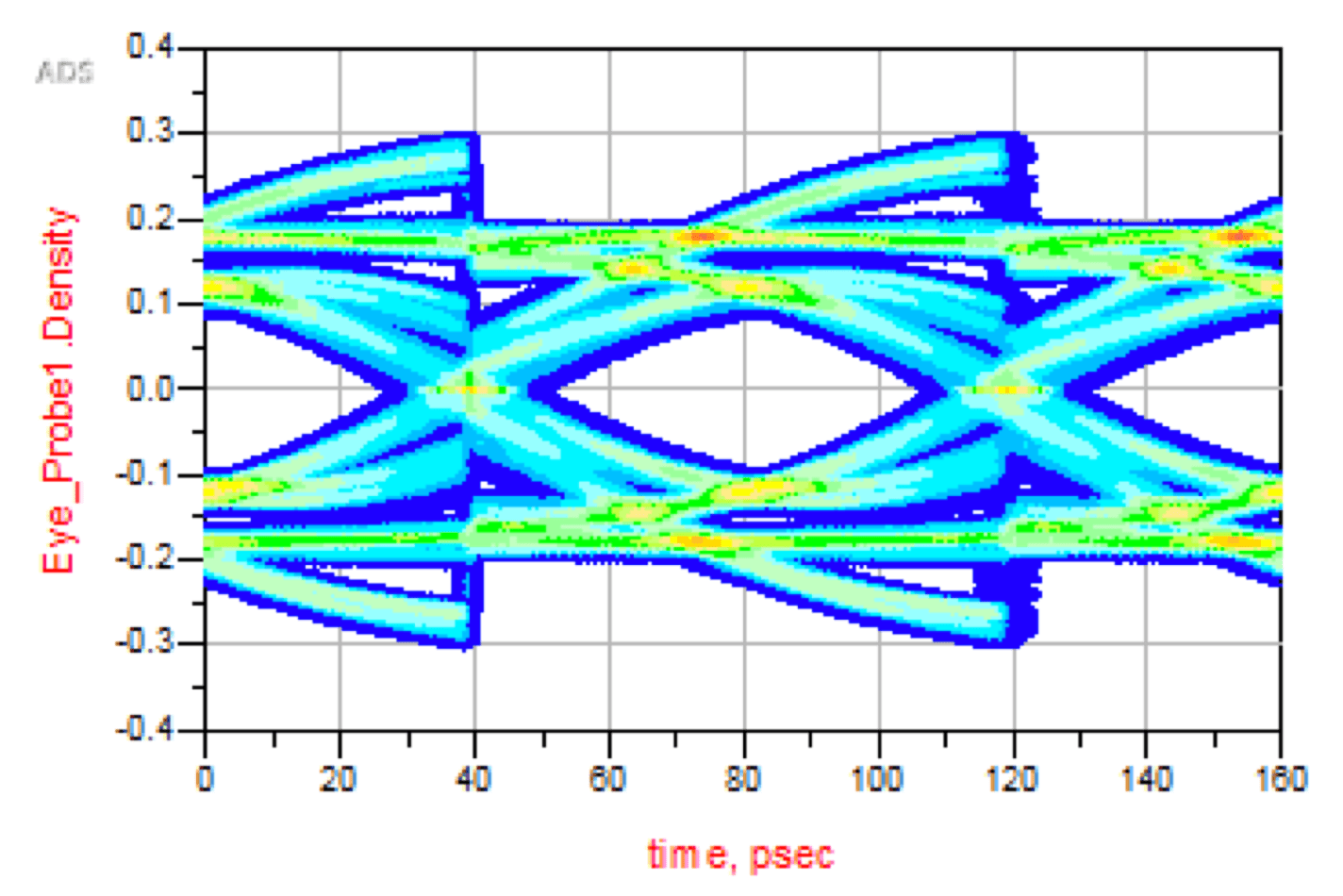

Goal: Go beyond state-of-the-art performance on a VPX backplane and achieve 100Gbps data throughput (25 Gbps per differential pair)

Goal: go beyond state-of-the-art performance on a VPX backplane and achieve 100Gbps data throughput (25 Gbps per differential pair)

Challenge:

Result: The first revision of 5 slot 6U VPX backplane with distributed architecture was successfully characterized in compliance with IEEE 802.3bj 100Gb/s Ethernet specification. No further redesign was needed.

How it was done:

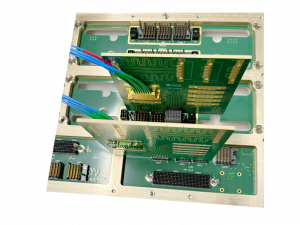

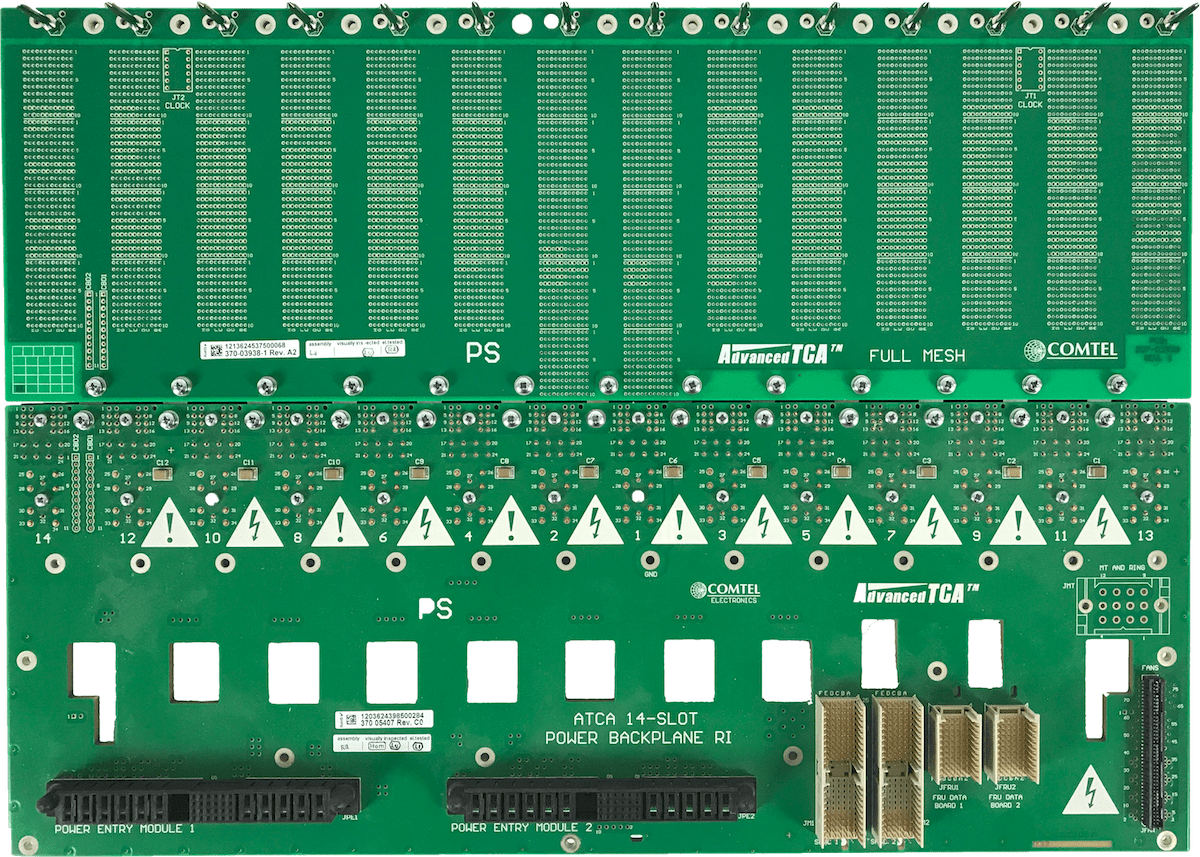

Goal: Design 14 slot ATCA full mesh backplane that is compliant with IEEE 802.3bj 100Gb/s Ethernet specifications and with corresponding PICMG 3.1R3.0 100Gb/s Ethernet specifications. Use original ZD connectors (not ZD+ or ZDPro)

Goal: design 14 slot ATCA full mesh backplane that is compliant with IEEE 802.3bj 100Gb/s Ethernet specifications and with corresponding PICMG 3.1R3.0 100Gb/s Ethernet specifications. Use original ZD connectors (not ZD+ or ZDPro)

Challenge:

Result:

How it was done:

Goal: Eliminate a typical trade-off between power and high-speed performance when designing a 14 slot ATCA backplane

Goal: eliminate a typical trade-off between power and high-speed performance when designing a 14 slot ATCA backplane

Challenge:

Result:

How it was done:

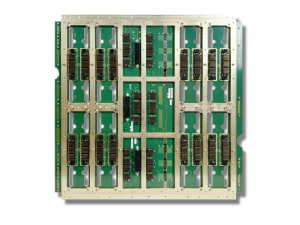

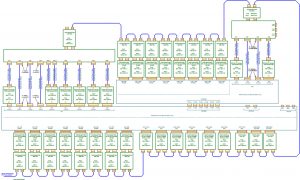

Goal: Backplane for 20 FPGA-based modules with 320 Aurora links between FPGAs, Aurora links at 28Gbps and clock skew less than 1ps, 6kW power consumption of all modules, 0.6m x 0.65m backplane size, Quality for military use